# **OpenMP and Performance**

Christian Terboven, Dirk Schmidl IT Center, RWTH Aachen University Member of the HPC Group {terboven,schmidl}@itc.rwth-aachen.de

IT Center der RWTH Aachen University

Performance Tuning aims to improve the runtime of an existing application.

2

#### **Hotspots**

3

A Hotspot is a source code region where a significant part of the runtime is spent.

| 90/10 law                                                  |    |

|------------------------------------------------------------|----|

| 90% of the runtime in a program is spent in 10% of the cod | e. |

Hotspots can indicate where to start with serial optimization or shared memory parallelization.

Use a tool to identify hotspots. In many cases the results are surprising.

# **Performance Tools**

4

# **VTune Amplifier XE**

#### Performance Analyses for

- → Serial Applications

- → Shared Memory Parallel Applications

- Sampling Based measurementsFeatures:

- → Hot Spot Analysis

- → Concurrency Analysis

- → Wait

5

→ Hardware Performance Counter Support

#### **Stream**

- Standard Benchmark to measure memory performance.

- Version is parallelized with OpenMP.

**Measures Memory bandwidth for:**

y=x (copy) y=s\*x (scale) y=x+z (add) y=x+s\*z (triad) #pragma omp parallel for for (j=0; j<N; j++) b[j] = scalar\*c[j];

#### for double vectors x,y,z and scalar double value s

| Functior | n Rate (MB/s) | Avg time | Min time | Max time |

|----------|---------------|----------|----------|----------|

| Сору:    | 33237.0185    | 0.0050   | 0.0048   | 0.0055   |

| Scale:   | 33304.6471    | 0.0049   | 0.0048   | 0.0059   |

| Add:     | 35456.0586    | 0.0070   | 0.0068   | 0.0073   |

| Triad:   | 36030.9600    | 0.0069   | 0.0067   | 0.0072   |

**OpenMP and Performance**

C. Terboven | IT Center der RWTH Aachen University

6

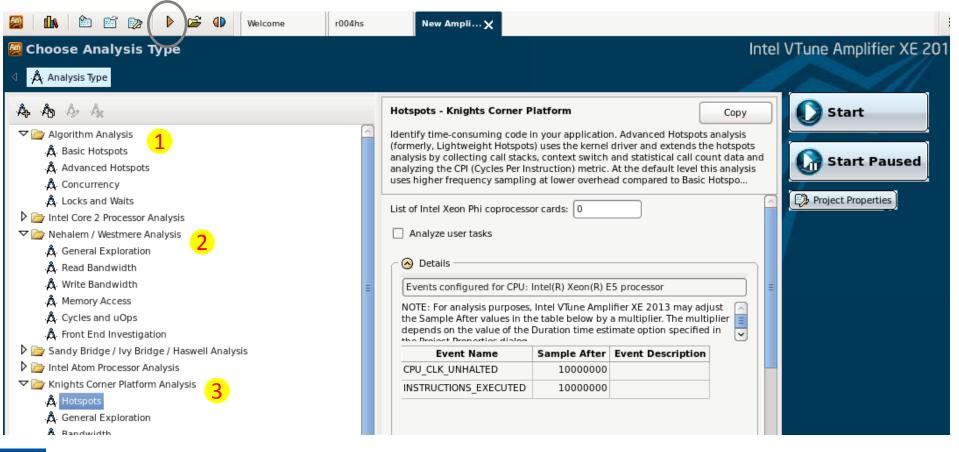

# **Amplifier XE – Measurement Runs**

- 1 Basic Analysis Types

- 2 Hardware Counter Analysis Types, choose Nehalem Architecture, on cluster-linux-tuning.

- 3 Analysis for Intel Xeon Phi coprocessors, choose this for OpenMP target programs.

**OpenMP and Performance**

7

C. Terboven | IT Center der RWTH Aachen University

# **Amplifier XE – Hotspot Analysis**

Double clicking on a function opens source code view.

- **1** Source Code View (only if compiled with -g)

- 2 Hotspot: Add Operation of Stream

- 3 Metrics View

| Sour | ce Assembly 📄 🕾 🖓 🎲 🎝 🛽                                               |             |     | ]       |

|------|-----------------------------------------------------------------------|-------------|-----|---------|

| Line | Source                                                                | CPU Time 😽  | ^   |         |

| 238  | #else                                                                 |             |     |         |

| 239  | #pragma omp parallel for                                              | 0.010s[     |     |         |

| 240  | for (j=0; j≺N; j++)                                                   | 0.140s      |     |         |

| 241  | c[j] = a[j]+b[j]; 2                                                   | 2.790s      |     |         |

| 242  | #endif                                                                |             |     | -       |

| 243  | <pre>times[2][k] = mysecond() - times[2][k];</pre>                    |             |     |         |

| 244  |                                                                       |             |     |         |

| 245  | <pre>times[3][k] = mysecond();</pre>                                  |             |     |         |

| 246  | #ifdef TUNED                                                          |             | _ = |         |

| 247  | <pre>tuned_STREAM_Triad(scalar);</pre>                                |             | =   |         |

| 248  | #else                                                                 |             |     | Hotspot |

| 249  | #pragma omp parallel for                                              |             |     |         |

| 250  | for (j=0; j <n; j++)<="" td=""><td>0.160s</td><td></td><td></td></n;> | 0.160s      |     |         |

| 251  | a[j] = b[j]+scalar*c[j];                                              | 2.751s      |     |         |

| 252  | #endif                                                                |             |     |         |

| 253  | <pre>times[3][k] = mysecond() - times[3][k];</pre>                    | 3           |     |         |

| 254  | }                                                                     |             |     |         |

| 200  | Selected 1 row(s):                                                    | 2.790s      | ~   |         |

| (    | < <u>()</u> >                                                         | < <u>00</u> |     |         |

**OpenMP and Performance**

C. Terboven | IT Center der RWTH Aachen University

# **Load Balancing**

OpenMP and Performance C. Terboven | IT Center der RWTH Aachen University

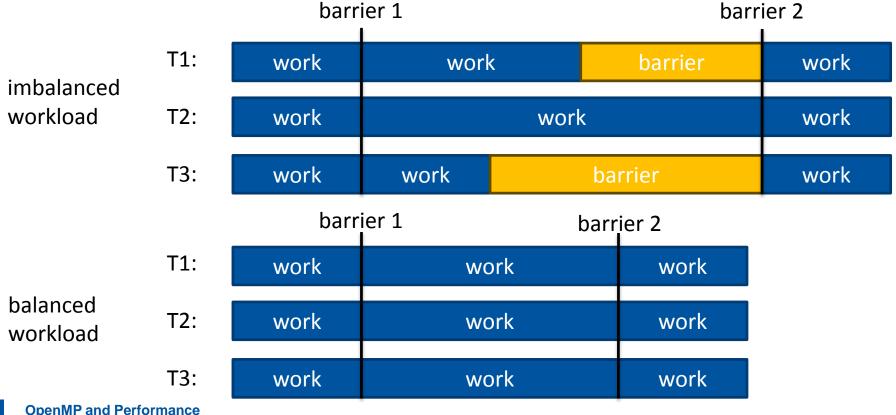

## Load imbalance

#### Load imbalance occurs in a parallel program

- $\rightarrow$  when multiple threads synchronize at global synchronization points

- $\rightarrow$  and these threads need a different amount of time to finish the calculation.

**C. Terboven** | IT Center der RWTH Aachen University

10

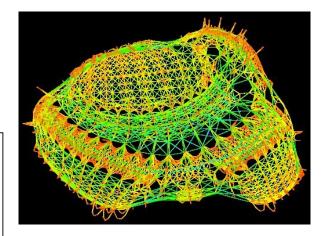

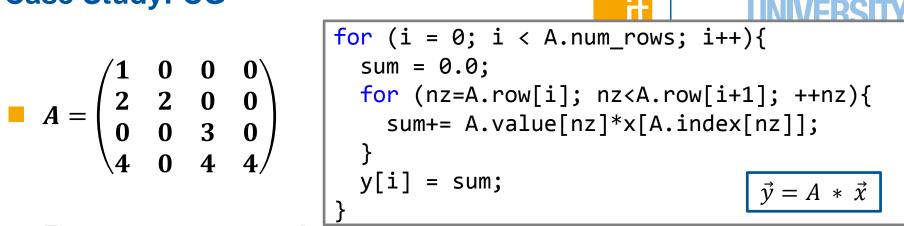

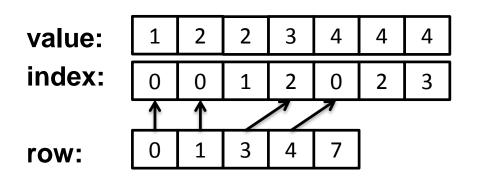

# **Case Study: CG**

#### Sparse Linear Algebra

- → Sparse Linear Equation Systems occur in many scientific disciplines.

- → Sparse matrix-vector multiplications (SpMxV) are the dominant part in many iterative solvers (like the CG) for such systems.

- number of non-zeros << n\*n</p>

11

# Beijing Botanical Garden

| Oben Rechts:  | Orginal Gebäude |

|---------------|-----------------|

| Unten Rechts: | Modell          |

| Unten Links:  | Matrix          |

(Quelle: Beijing Botanical Garden and University of Florida, Sparse Matrix Collection)

## **Case Study: CG**

Format: compressed row storage

store all values and columns in arrays (length nnz)

store beginning of a new row in a third array (length n+1)

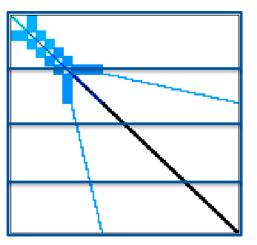

## Load Imbalance in VTune

- Grouping execution time of parallel regions by threads helps to detect load imbalance.

- Significant potions of Spin Time also indicate load balance problems.

- Different loop schedules might help to avoid these problems.

| 💹 Basic Hotspots Hotspots by CPU                             | J Usage viewpoint ( <u>change</u> ) ⑦ |            |                        |                    |               |               |

|--------------------------------------------------------------|---------------------------------------|------------|------------------------|--------------------|---------------|---------------|

| 🔄 \ominus Analysis Target 🛝 Analysis Type 🔛 Coll             | lection Log 🛛 🕅 Summary 😪 Bottom-up   | 🖧 Caller/0 | Callee 🗳 Top-down Tree | e 🔣 Tasks and Fram | ies           |               |

| Grouping: Process / Function / Thread / Call Stack           |                                       |            |                        |                    |               |               |

| Process / Function / Thread / Call Stack                     | CPU Time by Utilization               | 🛠 📎        | Overhead and S         |                    |               |               |

|                                                              | 🗍 Idle 📕 Poor 📋 Ok 📕 Ideal 📕 Over     | Ī          | Overhead Time          | Spin Time          | Module        | Start Address |

| ▼kernel_smxv-FAST.exe                                        | 23.373s                               |            | 0s                     | 7.546s             |               | 0             |

| Trun_loop\$omp\$parallel_for@95                              | 14.906s                               |            | 0s                     | 0s                 | kernel_smxv-F | 0x40e04e      |

| ▶_start (TID: 28437)                                         | 3.708s                                |            | 0s                     | 0s                 | kernel_smxv-F | 0x40e04e      |

| OMP Worker Thread #1 (TID: 28583)                            | 2.810s                                |            | 0s                     | 0s                 | kernel_smxv-F | 0x40e04e      |

| OMP Worker Thread #2 (TID: 28584)                            | 2.639s                                |            | 0s                     | 0s                 | kernel_smxv-F | 0x40e04e      |

| OMP Worker Thread #3 (TID: 28585)                            | 2.319s                                |            | 0s                     | 0s                 | kernel_smxv-F | 0x40e04e      |

| OMP Worker Thread #4 (TID: 28586)                            | 1.720s                                |            | 0s                     | 0s                 | kernel_smxv-F | 0x40e04e      |

| OMP Worker Thread #5 (TID: 28587)                            | 1.710s                                |            | 0s                     | 0s                 | kernel_smxv-F | 0x40e04e      |

| ↓[OpenMP worker]                                             | 7.536s                                |            | 0s                     | 7.536s             | libiomp5.so   | 0x8bf70       |

| ♦ run_loop\$omp\$parallel_for@45                             | 0.891s                                |            | 0s                     | 0s                 | kernel_smxv-F | 0x40e5da      |

| ▷laperf::load_drops_matlab_matrix <double, int=""></double,> | 0.030s                                |            | 0s                     | 0s                 | kernel_smxv-F | 0x41d570      |

| ▷[OpenMP fork]                                               | 0.010s                                |            | 0s                     | 0.010s             | libiomp5.so   | 0x46d80       |

13

C. Terboven | IT Center der RWTH Aachen University

# Load Imbalance in VTune

#### The Timeline can help to investigate the problem further.

#### Zooming in, e.g. to one iteration is also possible.

14 OpenMP and Performance

C. Terboven | IT Center der RWTH Aachen University

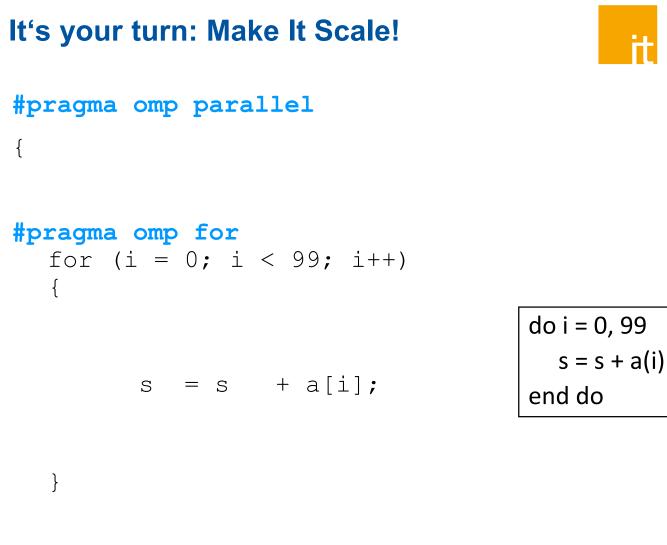

# **Parallel Loop Scheduling**

**OpenMP and Performance C. Terboven**| IT Center der RWTH Aachen University

# **Load Balancing**

# **Influencing the For Loop Scheduling**

- *for*-construct: OpenMP allows to influence how the iterations are scheduled among the threads of the team, via the *schedule* clause:

- → schedule(static [, chunk]): Iteration space divided into blocks of chunk size, blocks are assigned to threads in a round-robin fashion. If chunk is not specified: #threads blocks.

- → schedule (dynamic [, chunk]): Iteration space divided into blocks of chunk (not specified: 1) size, blocks are scheduled to threads in the order in which threads finish previous blocks.

- Schedule(guided [, chunk]): Similar to dynamic, but block size starts with implementation-defined value, then is decreased exponentially down to chunk.

- Default on most implementations is schedule (static).

17 **OpenMP and Performance C. Terboven**| IT Center der RWTH Aachen University

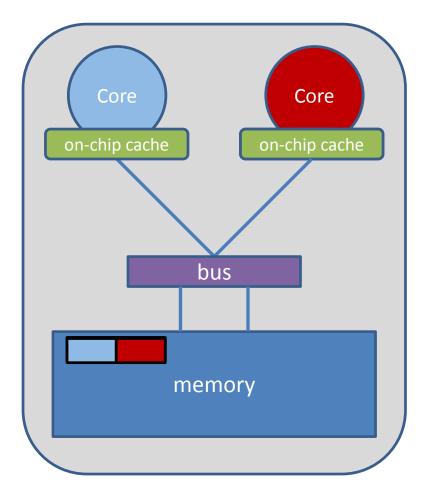

# **False Sharing**

# Caches

# CPU is fast

→ Order of 3.0 GHz

#### Caches:

- → Fast, but expensive

- → Thus small, order of MB

#### Memory is slow

- → Order of 0.3 GHz

- → Large, order of GB

# A good utilization of caches is crucial for good performance of HPC applications!

19 **OpenMP and Performance C. Terboven**| IT Center der RWTH Aachen University

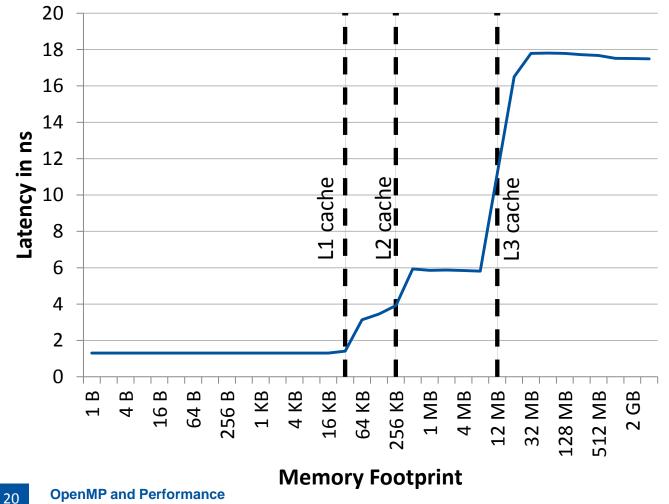

#### Visualization of the Memory Hierarchy

#### Latency on the Intel Westmere-EP 3.06 GHz processor

C. Terboven | IT Center der RWTH Aachen University

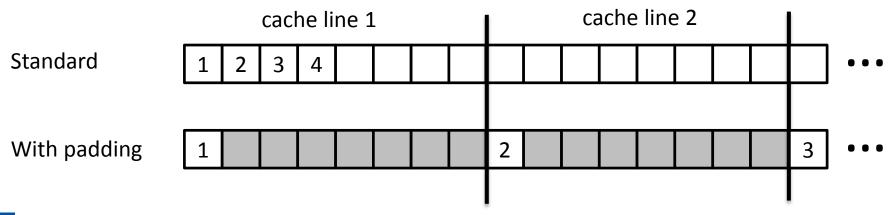

# Data in Caches

- The hardware always copies chunks into the cache, so called cache-lines.

- This is useful, when:

- the data is used frequently (temporal locality)

- → consecutive data is used which is on the same cache-line (spatial locality)

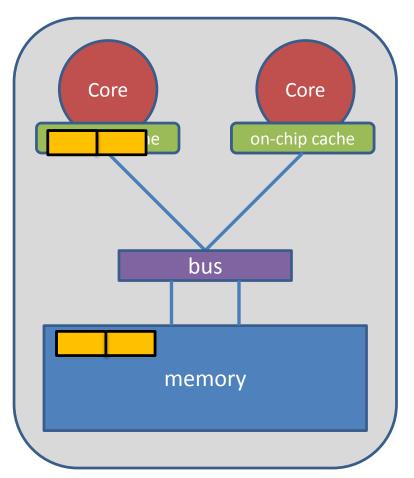

# **False Sharing**

#### False Sharing occurs when

- different threads use elements of the same cache-line

- one of the threads writes to the cache-line

- As a result the cache line is moved between the threads, also there is no real dependency

- Note: False Sharing is a performance problem, not a correctness issue

22

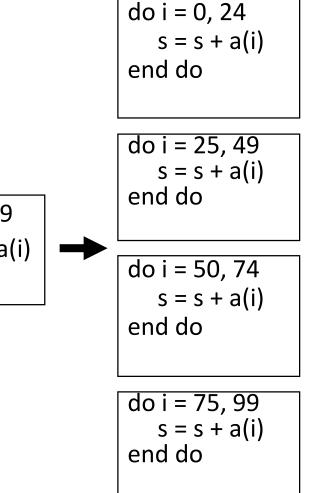

# Summing up vector elements again

OpenMP and Performance

C. Terboven | IT Center der RWTH Aachen University

# } // end parallel

# **False Sharing**

```

double s priv[nthreads];

#pragma omp parallel num threads(nthreads)

{

int t=omp get thread num();

#pragma omp for

for (i = 0; i < 99; i++)

{

s priv[t] += a[i];

}

} // end parallel

for (i = 0; i < nthreads; i++)

{

s += s priv[i];

```

# **False Sharing**

- no performance benefit for more threads

- Reason: false sharing of s\_priv

- Solution: padding so that only one variable per cache line is used

----with false-<del>shawing</del> fa<del>lse</del> windring</del> false sharing

# **False Sharing avoided**

```

double s priv[nthreads * 8];

#pragma omp parallel num threads(nthreads)

{

int t=omp get thread num();

#pragma omp for

for (i = 0; i < 99; i++)

{

s priv[t * 8] += a[i];

}

} // end parallel

for (i = 0; i < nthreads; i++)

{

s += s priv[i * 8];

```

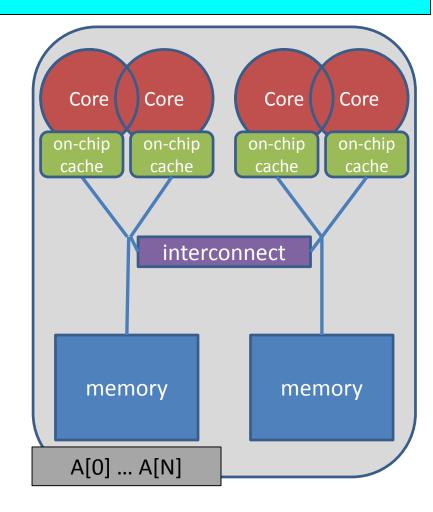

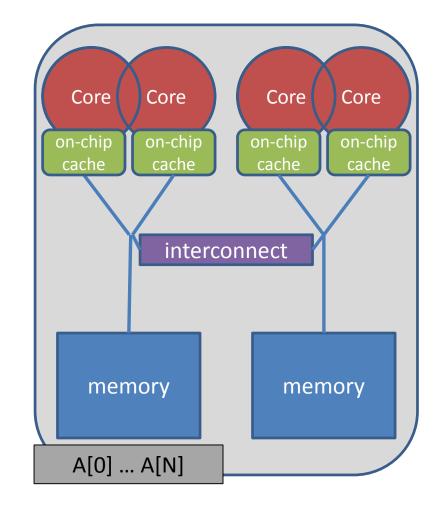

# **NUMA Architectures**

OpenMP and Performance C. Terboven | IT Center der RWTH Aachen University

# **Non-Uniform Memory Arch.**

# How To Distribute The Data ?

```

double* A;

A = (double*)

malloc(N * sizeof(double));

for (int i = 0; i < N; i++) {

A[i] = 0.0;

}

```

29 OpenMP and Performance C. Terboven | IT Center der RWTH Aachen University

# **About Data Distribution**

#### Important aspect on cc-NUMA systems

- $\rightarrow$  If not optimal, longer memory access times and hotspots

- OpenMP does not provide support for cc-NUMA

Placement comes from the Operating System

- → This is therefore Operating System dependent

Windows, Linux and Solaris all use the "First Touch" placement policy by default

→ May be possible to override default (check the docs)

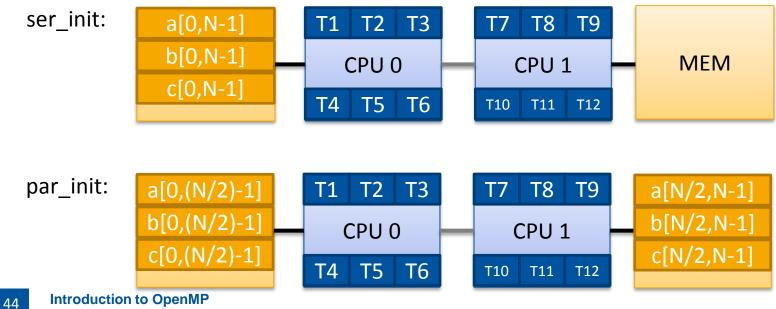

## **Non-Uniform Memory Arch.**

Serial code: all array elements are allocated in the memory of the NUMA node containing the core executing this thread

```

double* A;

A = (double*)

malloc(N * sizeof(double));

for (int i = 0; i < N; i++) {

A[i] = 0.0;

}

```

31 **OpenMP and Performance C. Terboven** | IT Center der RWTH Aachen University

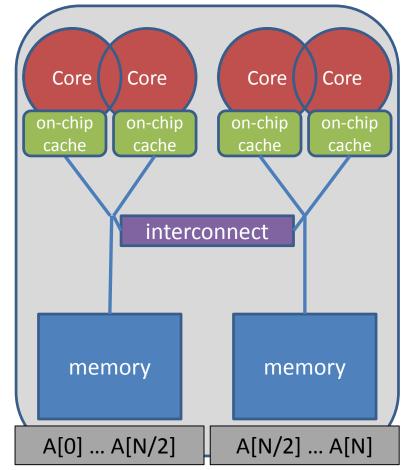

# **Non-Uniform Memory Arch.**

First Touch w/ parallel code: all array elements are allocated in the memory of the NUMA node containing the core executing the thread initializing the respective partition

```

double* A;

A = (double*)

malloc(N * sizeof(double));

omp_set_num_threads(2);

#pragma omp parallel for

for (int i = 0; i < N; i++) {

A[i] = 0.0;

```

}

# **Get Info on the System Topology**

- Before you design a strategy for thread binding, you should have a basic understanding of the system topology. Please use one of the following options on a target machine:

- → Intel MPI's cpuinfo tool

- $\rightarrow$  module switch openmpi intelmpi

- → cpuinfo

- →Delivers information about the number of sockets (= packages) and the mapping of processor ids used by the operating system to cpu cores.

- → hwlocs'tools

- → lstopo (command line: hwloc-ls)

- →Displays a graphical representation of the system topology, separated into NUMA nodes, along with the mapping of processor ids used by the

- operating system to cpu cores and additional info on caches.

C. Terboven | IT Center der RWTH Aachen University

# **Decide for Binding Strategy**

- Selecting the "right" binding strategy depends not only on the topology, but also on the characteristics of your application.

- $\rightarrow$  Putting threads far apart, i.e. on different sockets

- May improve the aggregated memory bandwidth available to your application

- $\rightarrow$  May improve the combined cache size available to your application

- → May decrease performance of synchronization constructs

- → Putting threads close together, i.e. on two adjacent cores which possibly shared some caches

- $\rightarrow$  May improve performance of synchronization constructs

- $\rightarrow$  May decrease the available memory bandwidth and cache size

- If you are unsure, just try a few options and then select the best one.

OpenMP and Performance C. Terboven | IT Center der RWTH Aachen University

34

**OpenMP 4.0: Places + Binding Policies (1/2)**

#### Define OpenMP Places

- $\rightarrow$  set of OpenMP threads running on one or more processors

- → can be defined by the user, i.e. OMP\_PLACES=cores

#### **Define a set of OpenMP Thread Affinity Policies**

- → SPREAD: spread OpenMP threads evenly among the places

- → CLOSE: pack OpenMP threads near master thread

- → MASTER: collocate OpenMP thread with master thread

#### Goals

- $\rightarrow$  user has a way to specify where to execute OpenMP threads for

- → locality between OpenMP threads / less false sharing / memory bandwidth

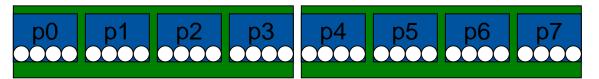

**Places**

#### Assume the following machine:

$\rightarrow$  2 sockets, 4 cores per socket, 4 hyper-threads per core

#### Abstract names for OMP\_PLACES:

- → threads: Each place corresponds to a single hardware thread on the target machine.

- → cores: Each place corresponds to a single core (having one or more hardware threads) on the target machine.

- → sockets: Each place corresponds to a single socket (consisting of one or more cores) on the target machine.

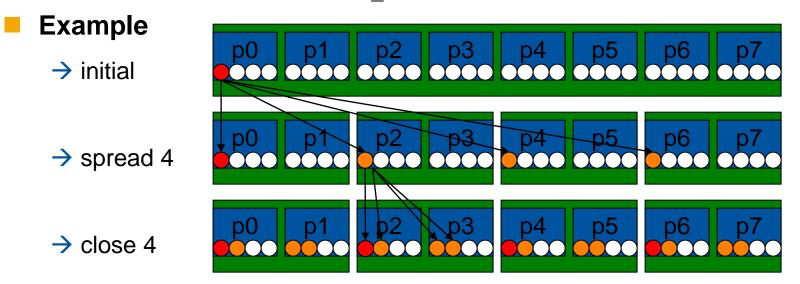

**OpenMP 4.0: Places + Binding Policies (2/2)**

# Example's Objective:

$\rightarrow$  separate cores for outer loop and near cores for inner loop

# Outer Parallel Region: proc\_bind(spread), Inner: proc\_bind(close)

→ spread creates partition, compact binds threads within respective partition OMP\_PLACES=(0,1,2,3), (4,5,6,7), ... = (0-3):8:4 = cores #pragma omp parallel proc\_bind(spread) #pragma omp parallel proc bind(close)

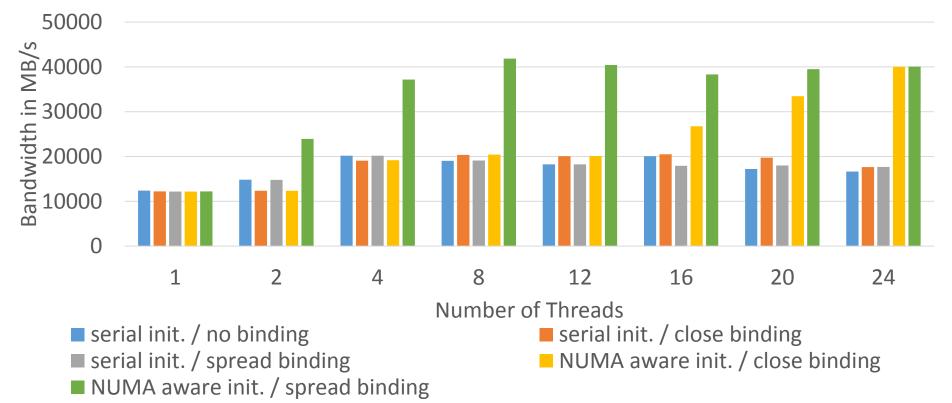

# **Serial vs. Parallel Initialization**

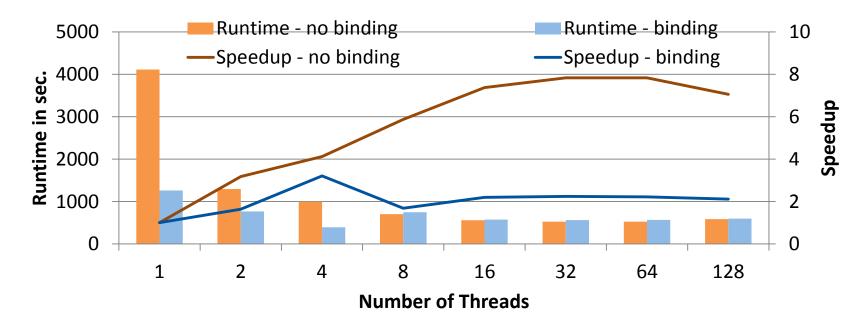

Performance of OpenMP-parallel STREAM vector assignment measured on 2-socket Intel® Xeon® X5675 ("Westmere") using Intel® Composer XE 2013 compiler with different thread binding options:

38

C. Terboven | IT Center der RWTH Aachen University

# **Detecting remote accesses**

39 **OpenMP and Performance C. Terboven** | IT Center der RWTH Aachen University

# **Hardware Counters**

#### **Definition: Hardware Performance Counters**

In computers, hardware performance counters, or hardware counters are a set of specialpurpose registers built into modern microprocessors to store the counts of hardwarerelated activities within computer systems. Advanced users often rely on those counters to conduct low-level performance analysis or tuning. (from: http://en.wikipedia.org)

## Hardware Performance Counters

#### Hardware Counters of our Intel Nehalem Processor:

SB DRAIN.ANY, STORE BLOCKS.AT RET, STOP MEM INST RETIRED.LOADS, MEM INST RET MEM\_UNCORE\_RETIRED.OTHE, MEM\_UNCOF FP COMP OPS EXE,SSE2 INT, FP COMP OP SIMD\_INT\_128.UNPACK, SIMD\_INT\_128.PACK INST QUEUE WRITES, INST DECODED.DECO, L2\_RQSTS.IFETCH\_HIT, L2\_RQSTS.IFETCH\_MIS L2 WRITE.RFO.S STATE, L2 WRITE.RFO.M ST

#### L1I.HITS: Counts all instruction fetches that hit the L1 L2\_PAGS IS.IFEICH\_HIT, L2\_RQS IS.IFEICH\_MIS L2\_DATA\_RQSTS.DEMAND.M\_, L2\_DATA\_RQS INStruction cache.

AD MISSES.PDE MIS, DTLB LOAD MISSES.LARGE W, MEM UNCORE RETIRED.L3 D, MP\_OPS\_EXE.MMX, FP\_COMP\_OPS\_EXE.SSE\_FP, NT 128.PACKED SHIFT, SIMD\_INT\_128.PACK, B, LOAD\_DISPATCH.ANY, ARITH.CYCLES\_DIV\_BUSY, HIT, L2 RQSTS.RFO MISS, L2 RQSTS.RFOS, S.DEMAND.S\_S, L2\_DATA\_RQSTS.DEMAND.E\_S, A\_RQSTS.PREFETCH.M, L2\_WRITE.RFO.I\_STATE, E, L2 WRITE.LOCK.HIT, L2 WRITE.LOCK.MESI,

L1D\_WB\_L2.I\_STATE, L1D\_WB\_L2.S\_STATE, L1D\_WB\_L2.E\_STATE, L1D\_WB\_L2.M\_STATE, L1D\_STATE, L LID CACHE LD.M STATE, LID CACHE LD.MESI, LID CACHE ST.S STATE, LID CACHE ST.E STATE, LID CACHE ST.M STATE, LID CACHE LOCK.HIT, LID CACHE LOCK.S STATE, LID CACHE LOCK.E STATE, LID CACHE LOCK.M STATE, LID CACHE STATE, LID CACHE LOCK.M STATE, LID CACHE STATE, LID L1D\_ALL\_REF.CACHEABLE, DTLB\_MISSES.ANY, DTLB\_MISSES.WALK\_COMPLET, DTLB\_MISSES.STLB\_HIT, DTLB\_MISSES.PDE\_MISS, DTLB\_MISSES.LARGE\_WALK\_C, LOAD\_HIT\_PRE, L1D\_PREFETCH.REQUESTS, L1D\_PREFETCH.MISS, L1D\_PREFETCH.TRIGGERS, L1D.M\_REPL, L1D.M\_EVICT, L1D.M\_SNOOP\_EVICT, L1D\_CACHE\_PREFETCH\_LOCK, L1D\_CACHE\_LOCK\_FB\_HIT, CACHE\_LOCK\_CYCLES.L1D\_L2, CACHE\_LOCK\_CYCLES.L1D, IO\_TRANSACTIONS, L1I.CYCLES\_STALLED, LARGE\_ITLB.HIT, ITLB\_MISSES.ANY, ITLB MISSES.WALK COMPLET, ILD STALL.LCP, ILD STALL.MRU, ILD STALL.RQ FULL, ILD STALL.REGEN, ILD STALL.ANY, BR INST EXEC.COND, BR INST EXEC.DIRECT, BR INST EXEC.INDIRECT NON, BR INST EXEC.NON CALLS, BR INST EXEC.RETURN NEA, BR\_INST\_EXEC.DIRECT\_NEAR, BR\_INST\_EXEC.INDIRECT\_NEA, BR\_INST\_EXEC.NEAR\_CALLS, BR\_INST\_EXEC.TAKEN, BR\_MISP\_EXEC.COND, BR\_MISP\_EXEC.DIRECT, BR\_MISP\_EXEC.INDIRECT\_NO, BR\_MISP\_EXEC.NON\_CALLS, BR\_INST\_EXEC.TAKEN, BR\_MISP\_EXEC.COND, BR\_MISP\_EXEC.DIRECT, BR\_MISP\_EXEC.INDIRECT\_NO, BR\_MISP\_EXEC.NON\_CALLS, BR\_INST\_EXEC.TAKEN, BR\_MISP\_EXEC.COND, BR\_MISP\_EXEC.DIRECT, BR\_MISP\_EXEC.INDIRECT\_NO, BR\_MISP\_EXEC.NON\_CALLS, BR\_INST\_EXEC.TAKEN, BR\_MISP\_EXEC.TAKEN, BR\_MISP\_EXEC.TAKEN, BR\_MISP\_EXEC.DIRECT, BR\_MISP\_EXEC.DIRECT, BR\_MISP\_EXEC.TAKEN, BR\_MISP\_EXEC.TAK BR MISP EXEC.DIRECT NEAR, BR MISP EXEC.INDIRECT NEA, BR MISP EXEC.NEAR CALLS, BR MISP EXEC.TAKEN, RESOURCE STALLS.ANY, RESOURCE STALLS.LOAD, RESOURCE STALLS.RS FULL, RESOURCE STALLS.STORE, RESOURCE STALLS.ROB FULL, RESOURCE STALLS.FPCW, RESOURCE STALLS.MXCSR, RESOURCE STALLS.OTHER, MACRO INSTS.FUSIONS DECO, BACLEAR FORCE IQ, ITLB FLUSH, OFFCORE REQUESTS.L1D WR, UOPS EXECUTED.PORT0, UOPS EXECUTED.PORT1, UOPS\_EXECUTED.PORT2\_COR, UOPS\_EXECUTED.PORT3\_COR, UOPS\_EXECUTED.PORT4\_COR, UOPS\_EXECUTED.PORT5, UOPS\_EXECUTED.PORT015, UOPS\_EXECUTED.PORT234, OFFCORE\_REQUESTS\_SQ\_FUL, OFF\_CORE\_RESPONSE\_0, SNOOP\_RESPONSE.HIT, SNOOP RESPONSE.HITE, SNOOP RESPONSE.HITE, SNOOP RESPONSE 1, INST RETIRED, ANY P. INST RETIRED, X87, INST RETIRED, MMX, UOPS RETIRED, ANY, UOPS RETIRED, RETIRED, RETIRED, MACRO FUSE, MACHINE CLEARS, CYCLES, MACHINE\_CLEARS.MEM\_ORDE, MACHINE\_CLEARS.SMC, BR\_INST\_RETIRED.ALL\_BRAN, BR\_INST\_RETIRED.CONDITION, BR\_INST\_RETIRED.NEAR\_CAL, BR\_MISP\_RETIRED.ALL\_BRAN, BR\_MISP\_RETIRED.NEAR\_CAL, SEX\_UOPS\_RETIRED.PACKED, SSEX UOPS RETIRED.SCALAR, SSEX UOPS RETIRED.PACKED, SSEX UOPS RETIRED.SCALAR, SSEX UOPS RETIRED.VECTOR, ITLB MISS RETIRED, MEM LOAD RETIRED.L12 HIT, MEM LOAD RETIRED.24 HIT, MEM LOAD RETIRED.13 UNS, MEM LOAD RETIRED.OTHER , MEM LOAD RETIRED.13 MISS, MEM LOAD RETIRED.HIT LFB, MEM LOAD RETIRED.DTLB MI, FP MMX TRANS.TO FP, FP MMX TRANS.TO MMX, FP MMX TRANS.ANY, MACRO INSTS.DECODED, UOPS DECODED.MS, UOPS\_DECODED.ESP\_FOLDING, UOPS\_DECODED.ESP\_SYNC, RAT\_STALLS.FLAGS, RAT\_STALLS.REGISTERS, RAT\_STALLS.ROB\_READ\_POR, RAT\_STALLS.SCOREBOARD, RAT\_STALLS.ANY, SEG\_RENAME\_STALLS, ES\_REG\_RENAMES, UOP\_UNFUSION, BR INST DECODED, BPU MISSED CALL RET, BACLEAR.BAD TARGET, BPU CLEARS.EARLY, BPU CLEARS.LATE, L2 TRANSACTIONS.IOAD, L2 TRANSACTIONS.RFO, L2 TRANSACTIONS.IFETCH, L2 TRANSACTIONS.PREFETCH, L2 TRANSACTIONS.LATE, L2 TRANSACTIONS.LATE, L2 TRANSACTIONS.PREFETCH, L2 TRANSACTIONS.PREF L2\_TRANSACTIONS.FILL, L2\_TRANSACTIONS.WB, L2\_TRANSACTIONS.ANY, L2\_LINES\_IN.S\_STATE, L2\_LINES\_IN.E\_STATE, L2\_LINES\_IN.ANY, L2\_LINES\_OUT.DEMAND\_CLEA, L2\_LINES\_OUT.DEMAND\_DIRT, L2\_LINES\_OUT.PREFETCH\_CLE, L2 LINES OUT.PREFETCH DIR, L2 LINES OUT.ANY, SQ MISC.SPLIT LOCK, SQ FULL STALL CYCLES, FP ASSIST.ALL, FP ASSIST.OUTPUT, FP ASSIST.INPUT, SIMD INT 64.PACKED MPY, SIMD INT 64.PACKED SHIFT, SIMD INT 64.P SIMD INT 64.UNPACK, SIMD INT 64.PACKED LOGICA, CPUID, SIMD INT 64.PACKED ARITH, SIMD INT 64.SHUFFLE MOVE, UNC GQ CYCLES FULL.READ , UNC GQ CYCLES FULL.WRITE, UNC GQ CYCLES FULL.PEER , UNC GQ CYCLES NOT EMPTY, UNC\_GQ\_CYCLES\_NOT\_EMPTY, UNC\_GQ\_CYCLES\_NOT\_EMPTY, UNC\_GQ\_ALLOC.READ\_TRACK, UNC\_GQ\_ALLOC.RT\_13\_MISS, UNC\_GQ\_ALLOC.RT\_T0\_13\_RE, UNC\_GQ\_ALLOC.RT\_T0\_RTID\_, UNC\_GQ\_ALLOC.WT T0\_RTID, UNC\_GQ\_ALLOC.WRITE\_TRAC, UNC GQ ALLOC.PEER PROBE, UNC GQ DATA.FROM QPI, UNC GQ DATA.FROM QMC, UNC GQ DATA.FROM L3, UNC GQ DATA.FROM CORES , UNC GQ DATA.FROM CORES , UNC GQ DATA.TO QPI QMC, UNC GQ DATA.TO L3,

UNC\_GQ\_DATA.TO\_CORES, UNC\_SNP\_RESP\_ UNC SNP RESP TO REMOTE, UNC SNP RES UNC L3 HITS.ANY, UNC L3 MISS.READ, UNC UNC\_L3\_LINES\_OUT.M\_STATE, UNC\_L3\_LINE UNC QHL REQUESTS.REMOTE, UNC QHL RE UNC\_QHL\_CYCLES\_NOT\_EMPT, UNC\_QHL\_CY UNC QHL CONFLICT CYCLES., UNC QHL CO UNC QMC NORMAL FULL.WRI, UNC QMC UNC\_QMC\_BUSY.READ.CH1, UNC\_QMC\_BUS UNC QMC ISSOC OCCUPANCY., UNC QMC UNC\_QMC\_NORMAL\_READS.A, UNC\_QMC\_H UNC QMC CRITICAL PRIORIT, UNC QMC W UNC\_QHL\_FRC\_ACK\_CNFLTS.L, UNC\_QPI\_TX\_ UNC QPI TX STALLED SINGL, UNC QPI TX

41

BR MISP EXEC.COND: Counts the number of mispredicted conditional near branch instructions executed, but not UNC\_QMC\_CRITICAL\_PRIORIT, UNC\_QMC\_W UNC\_QMC\_CANCEL.CHO, UNC\_QMC\_CANCEL NECESSARILY retired.

\_RESP\_TO\_LOCAL\_H, UNC\_SNP\_RESP\_TO\_REMOTE, HITS.READ, UNC L3 HITS.WRITE, UNC L3 HITS.PROBE, NC L3 LINES IN.F STATE, UNC L3 LINES IN.ANY, UESTS.IOH\_RE, UNC\_QHL\_REQUESTS.IOH\_WR, L CYCLES FULL.LOCA, UNC QHL CYCLES NOT EMPT, \_QHL\_ADDRESS\_CONFLIC, UNC\_QHL\_CONFLICT\_CYCLES.I, MC\_NORMAL\_FULL.WRI, UNC\_QMC\_NORMAL\_FULL.WRI, UNC QMC ISOC FULL.WRITE.C, UNC QMC BUSY.READ.CH0, CUPANCY.CH1, UNC\_QMC\_OCCUPANCY.CH2, , UNC QMC NORMAL READS.C, INC\_QMC\_CRITICAL\_PRIORIT, UNC\_QMC\_CRITICAL\_PRIORIT, MC WRITES.PARTIAL.C, UNC QMC WRITES.PARTIAL.C, TE, UNC QMC PRIORITY UPDATE, I\_TX\_STALLED\_SINGL, UNC\_QPI\_TX\_STALLED\_SINGL, QPI TX STALLED MULTI, UNC QPI TX STALLED MULTI,

UNC\_QPI\_TX\_HEADER.BUSY.LI, UNC\_QPI\_TX\_HEADER.BUSY.LI, UNC\_QPI\_RX\_NO\_PPT\_CREDI, UNC\_QPI\_RX\_NO\_PPT\_CREDI, UNC\_DRAM\_OPEN.CH0, UNC\_DRAM\_OPEN.CH1, UNC\_DRAM\_OPEN.CH2, UNC\_DRAM\_PAGE\_CLOSE.CH0, UNC DRAM PAGE CLOSE.CH1, UNC DRAM PAGE CLOSE.CH2, UNC DRAM PAGE MISS.CH0, UNC DRAM PAGE MISS.CH1, UNC DRAM PAGE MISS.CH2, UNC DRAM READ CAS.CH0, UNC DRAM READ CAS.CH1, UNC DRAM READ C UNC DRAM READ CAS.AUTO, UNC DRAM READ CAS.CH2, UNC DRAM READ CAS.AUTO, UNC\_DRAM\_WRITE\_CAS.CH0, UNC\_DRAM\_WRITE\_CAS.CH2, UNC DRAM\_WRITE\_CAS.AUTO, UNC\_DRAM\_WRITE\_CAS.CH2, UNC DRAM\_WRITE\_CAS.CH2, UNC DR UNC DRAM WRITE CAS.AUTO, UNC DRAM REFRESH.CHO

## **Derived Metrics**

# Clock cycles per Instructions (CPI)

- → CPI indicates if the application is utilizing the CPU or not

- → Take care: Doing "something" does not always mean doing "something useful".

## Floating Point Operations per second (FLOPS)

- → How many arithmetic operations are done per second?

- → Floating Point operations are normally really computing and for some algorithms the number of floating point operations needed can be determined.

1 CPI rate (Clock cycles per instruction): In theory modern processors can finish 4 instructions in 1 cycle, so a CPI rate of 0.25 is possible. A value between 0.25 and 1 is often considered as good for HPC applications.

1

### Elapsed Time: 1.872s

| Hardware Event Count:                                                                  | 125,574,000,000                                                                                                       |

|----------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------|

| CPU_CLK_UNHALTED.THREAD:                                                               | 6.3462e+10                                                                                                            |

| INST_RETIRED.ANY:                                                                      | 6.2112e+10                                                                                                            |

| CPI Rate:                                                                              | 1.022                                                                                                                 |

| The CPI may be too high. This could be<br>instructions. Explore the other hardwar      | 그는 이번 것을 물질 것 같아. 이번 방법에서 가장 같이 가지 않는 것이 것 같아. 가지 않는 것이 가지 않는 것이 없는 것이 없다. 것이 같이 많이 없다. |

| Retire Stalls: 🗇                                                                       | 0.570s                                                                                                                |

| A high number of retire stalls is detecter<br>issues. Use this metric to find where yo | 이 같은 것에서 집에 집에서 가려면 눈에 많은 것이 가지 않았다. 것 같은 것이 가지 않는 것이 같이 많이 많이 많이 많이 많이 많이 많이 많이 했다.                                  |

| LLC Miss:                                                                              | 0.013s                                                                                                                |

| LLC Load Misses Serviced By Remote DRA                                                 | M: 0.001s                                                                                                             |

| Instruction Starvation:                                                                | 0.098s                                                                                                                |

| Branch Mispredict:                                                                     | 0.001s                                                                                                                |

| Execution Stalls: OpenMP and Performance                                               | 0.288s                                                                                                                |

|                                                                                        |                                                                                                                       |

C. Terboven | IT Center der RWTH Aachen University

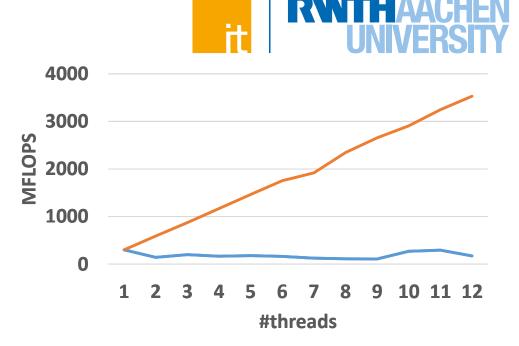

# **Counters for Remote Traffic**

Stream example ( $\vec{a} = \vec{b} + s * \vec{c}$ ) with and without parallel initialization.

$\rightarrow$  2 socket sytem with Xeon X5675 processors, 12 OpenMP threads

|          | сору      | scale     | add       | triad     |

|----------|-----------|-----------|-----------|-----------|

| ser_init | 18.8 GB/s | 18.5 GB/s | 18.1 GB/s | 18.2 GB/s |

| par_init | 41.3 GB/s | 39.3 GB/s | 40.3 GB/s | 40.4 GB/s |

Introduction to OpenMP

Dirk Schmidl, Christian Terboven | IT Center der RWTH Aachen University

# **Counters for Remote Traffic**

- Hardware counters can measure local and remote memory accesses.

- → MEM\_UNCORE\_RETIRED.LOCAL\_DRAM\_AND\_REMOTE\_CACHE\_HIT

accesses to local memory

→ MEM\_UNCORE\_RETIRED.REMOTE\_DRAM

accesses to remote memory

Absolute values are hard to interpret, but the ratio between both is useful.

## Detecting bad memory accesses for the stream benchmark.

| So    | Source Assembly                                                    |                                                    |                                |  |

|-------|--------------------------------------------------------------------|----------------------------------------------------|--------------------------------|--|

| So.   | Source                                                             | Hardware Event Count: Total by Hardware Event Type |                                |  |

| LI. 🗖 |                                                                    | MEM_UNCORE_RETIRED.LOCAL_DRAM_AND_REMOTE_CACHE_HIT | MEM_UNCORE_RETIRED.REMOTE_DRAM |  |

| 229   | #ifdef TUNED                                                       |                                                    |                                |  |

| 230   | <pre>tuned_STREAM_Scale(scalar);</pre>                             |                                                    |                                |  |

| 231   | #else                                                              |                                                    |                                |  |

| 232   | #pragma omp parallel for                                           |                                                    |                                |  |

| 233   | for (j=0; j <n; j++)<="" th=""><th>20,000</th><th>20,000</th></n;> | 20,000                                             | 20,000                         |  |

| 234   | <pre>b[j] = scalar*c[j];</pre>                                     | 3,820,000                                          | 3,940,000                      |  |

| 235   | #endif                                                             |                                                    |                                |  |

## Ratio of remote memory accesses:

|          | сору | scale | add  | triad |

|----------|------|-------|------|-------|

| ser_init | 52%  | 50%   | 50%  | 51%   |

| par_init | 0.5% | 1.7%  | 0.6% | 0.2%  |

Percentage of remote accesses for ser\_init and par\_init stream benchmark.

# **Case Study: CG Solver**

OpenMP and Performance

C. Terboven | IT Center der RWTH Aachen University

## Hotspot analysis of the serial code:

| Call Stack    | CPU Time: Total by Utilization    |  |  |

|---------------|-----------------------------------|--|--|

|               | 🔲 Idle 📕 Poor 📙 Ok 📕 Ideal 📘 Over |  |  |

| ≂ ≊ cg        | 46.7%                             |  |  |

| Þ ⊨ matvec    | 40.8% 1.                          |  |  |

| Þ ⊴ xpay      | 1.4% <b>2.</b>                    |  |  |

| Þ ⊴ axpy      | 1.4% <b>2.</b>                    |  |  |

| ▷ vectorDot   | 1.2% <b>3.</b>                    |  |  |

| Þ ≊ axpy      | 1.1% <b>2.</b>                    |  |  |

| ▷ > vectorDot | 0.6% <b>3.</b>                    |  |  |

## Hotspots are:

- 1. matrix-vector multiplication

- 2. scaled vector additions

- 3. dot product

48

OpenMP and Performance C. Terboven | IT Center der RWTH Aachen University

#### Tuning:

49

- parallelize all hotspots with a parallel for construct

- use a reduction for the dot-product

- activate thread binding

#### Hotspot analysis of naive parallel version:

#### **Event Name**

MEM\_UNCORE\_RETIRED.LOCAL\_DRAM\_AND\_REMOTE\_CACHE\_HIT

MEM\_UNCORE\_RETIRED.REMOTE\_DRAM

### A lot of remote accesses occur in nearly all places.

|                                                                | MEM_UNCORE_RETIRED.LOCAL | MEM_UNCORE_RETIRED.REMOTE |

|----------------------------------------------------------------|--------------------------|---------------------------|

| void matvec(const int n, const int                             |                          |                           |

| int i,j;                                                       |                          |                           |

| <pre>#pragma omp parallel for private(j)</pre>                 | 20,000                   | 0                         |

| for(i=0; i <n; i++){<="" td=""><td>0</td><td>0</td></n;>       | 0                        | 0                         |

| y[i]=0;                                                        | 0                        | 0                         |

| <pre>for(j=ptr[i]; j<ptr[i+1]; j<="" pre=""></ptr[i+1];></pre> | 6,740,000                | 3,720,000                 |

| y[i]+=value[j]*x[index[                                        | 17,580,000               | 6,680,000                 |

| }                                                              |                          |                           |

| }                                                              |                          |                           |

50 OpenMP and Performance

C. Terboven | IT Center der RWTH Aachen University

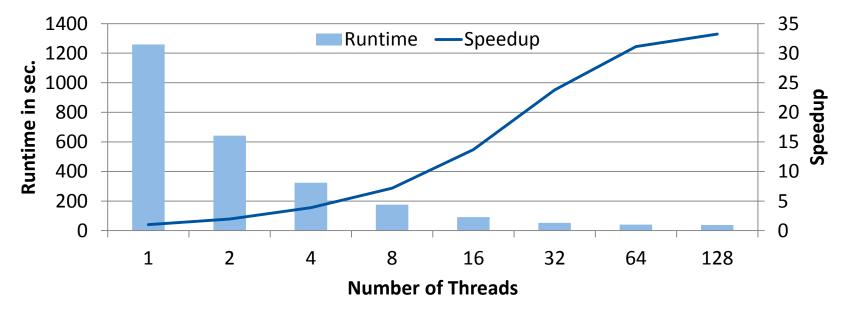

## Tuning:

- Initialize the data in parallel

- Add parallel for constructs to all initialization loops

Scalability improved a lot by this tuning on the large machine.

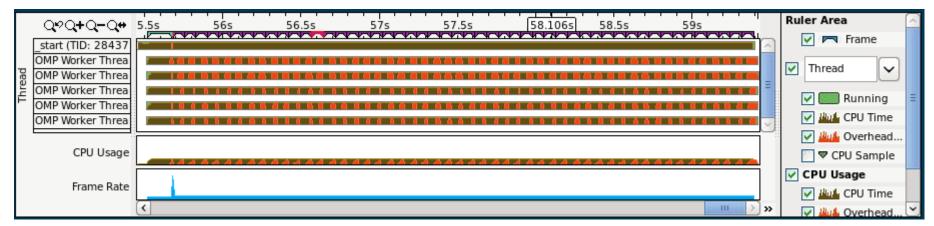

## Analyzing load imbalance in the concurrency view:

| So<br>Line | Source                                                                            | CPU Time: Total by 🔊                   | Ove 🔊   |

|------------|-----------------------------------------------------------------------------------|----------------------------------------|---------|

|            | Source                                                                            | 🔲 Idle 📕 Poor 📙 Ok 📕 Id <sup>and</sup> |         |

| 49         | void matvec(const int n, const int nnz,                                           |                                        |         |

| 50         | int i,j;                                                                          |                                        |         |

| 51         | <pre>#pragma omp parallel for private(j)</pre>                                    | 22.462s                                | 10.612s |

| 52         | for(i=0; i <n; i++){<="" td=""><td>0.050s</td><td>0s</td></n;>                    | 0.050s                                 | 0s      |

| 53         | y[i]=0;                                                                           | 0.060s                                 | 0s      |

| 54         | for(j=ptr[i]; j <ptr[i+1]; j++){<="" td=""><td>1.741s</td><td>0s</td></ptr[i+1];> | 1.741s                                 | 0s      |

| 55         | y[i]+=value[j]*x[index[j]];                                                       | 9.998s                                 | 0s      |

10 seconds out of ~35 seconds are overhead time

other parallel regions which are called the same amount of time only produce 1 second of overhead

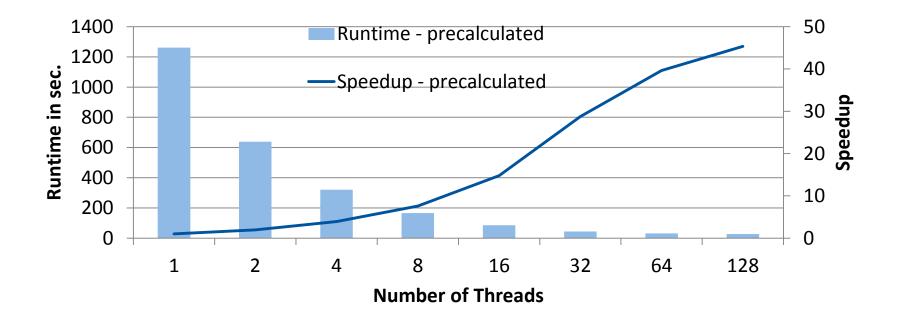

## Tuning:

53

→ pre-calculate a schedule for the matrix-vector multiplication, so that the nonzeros are distributed evenly instead of the rows

# **The Roofline Model**

OpenMP and Performance C. Terboven | IT Center der RWTH Aachen University

# When to stop tuning?

### Depends on many different factors:

- $\rightarrow$  How often is the code program used?

- $\rightarrow$  What are the runtime requirements?

- → Which performance can I expect?

Investigating kernels may help to understand larger applications.

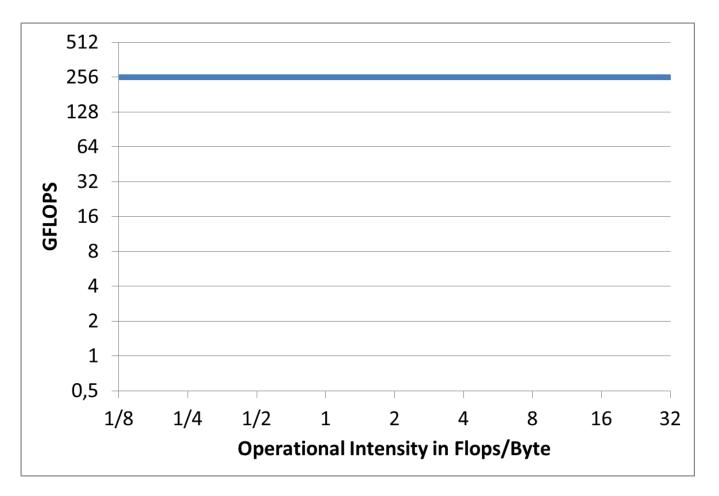

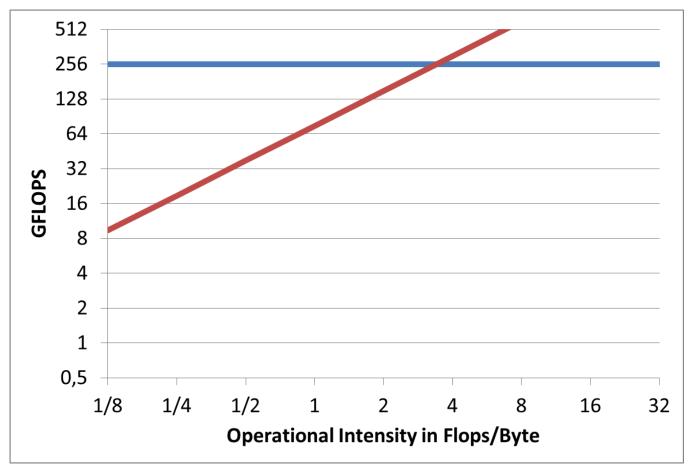

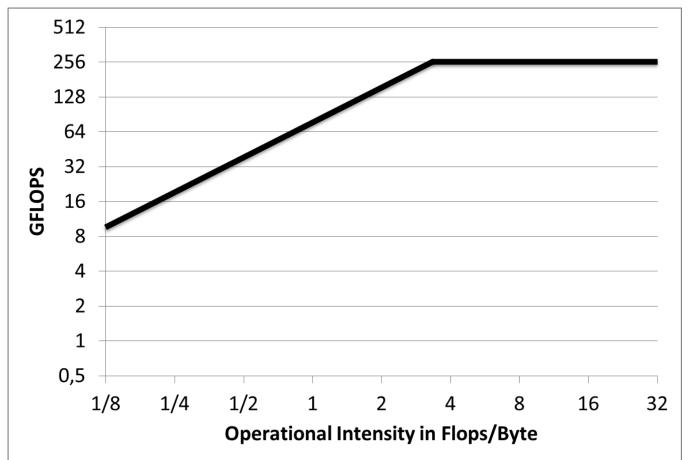

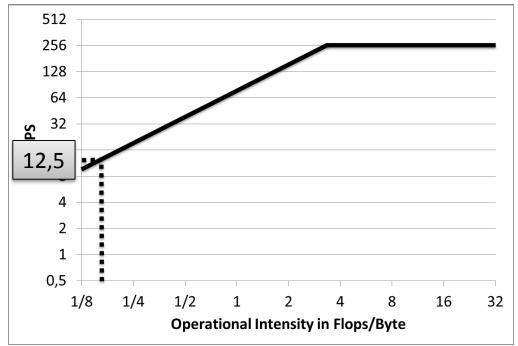

#### Peak performance of a 4 socket Nehalem Server is 256 GFLOPS.

# **Roofline Model**

## Memory bandwidth measured with Stream benchmark is about 75 GB/s.

57

# **Roofline Model**

The "Roofline" describes the peak performance the system can reach depending on the "operational intensity" of the algorithm.

# **Roofline Model**

**Example: Sparse Matrix Vector Multiplication y=Ax**

## Given:

- x and y are in the cache

- A is too large for the cache

measured performance was

12 GFLOPS

- 1 ADD and 1 MULT per element

- load of value (double) and index (int) per element

- -> 2 Flops / 12 Byte = 1/6 Flops/Byte

# **Questions?**